PLL (Phase-Locked Loop) to układ synchronizacji fazowej, będący sercem każdego nowoczesnego transceiverа. Dzięki PLL możesz precyzyjnie strojić częstotliwość z dokładnością do 1 Hz, co byłoby niemożliwe ze starym VFO.

Jak działa PLL?

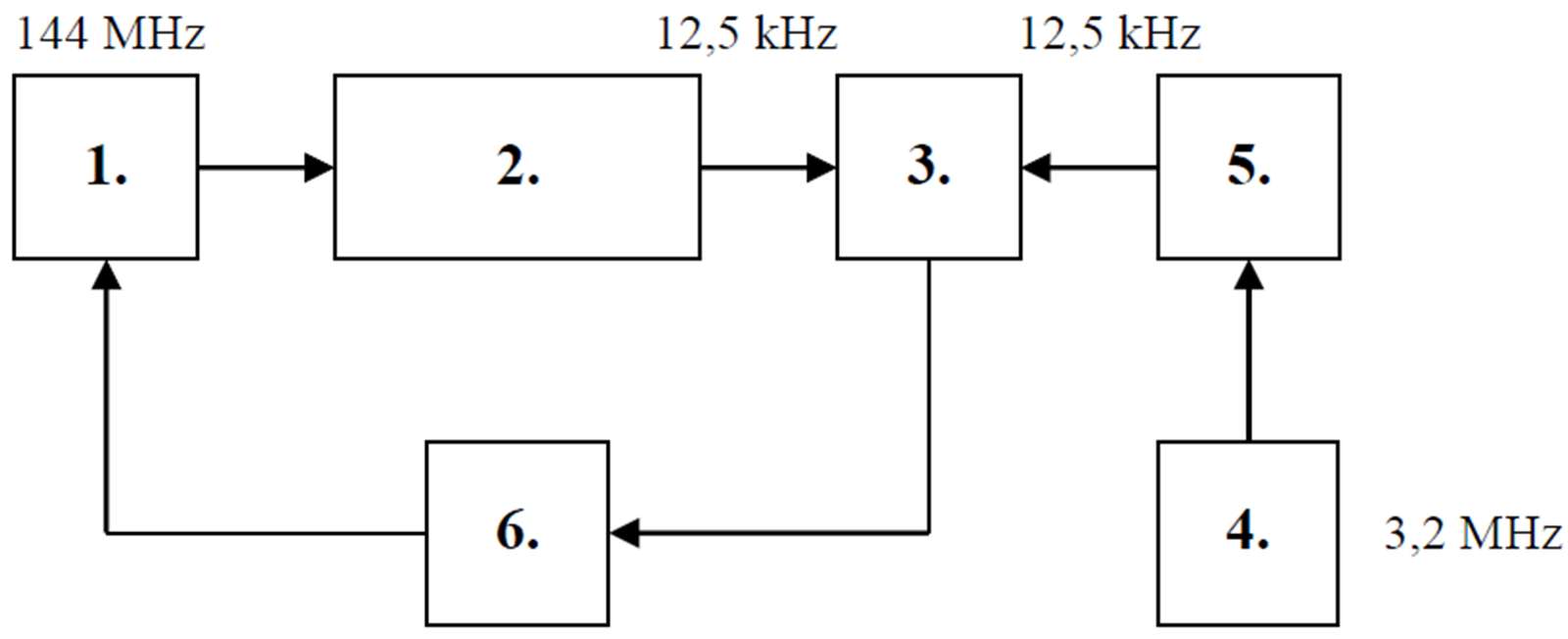

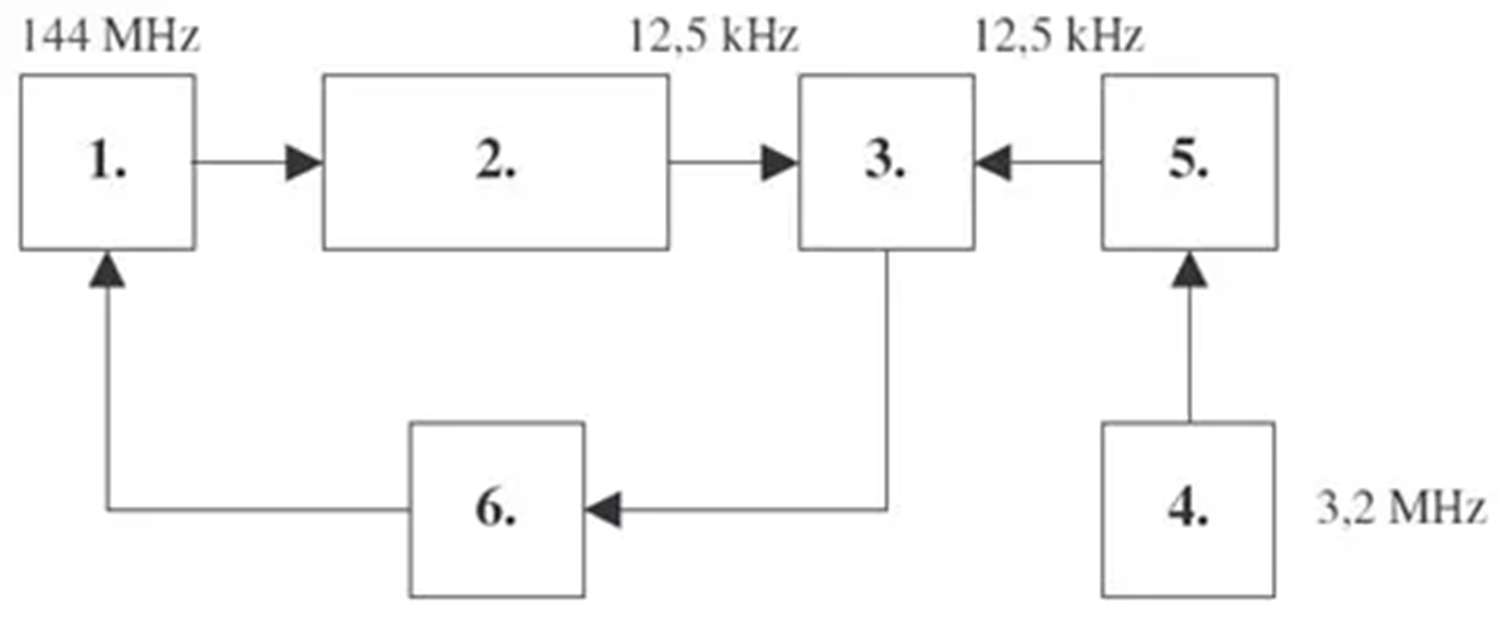

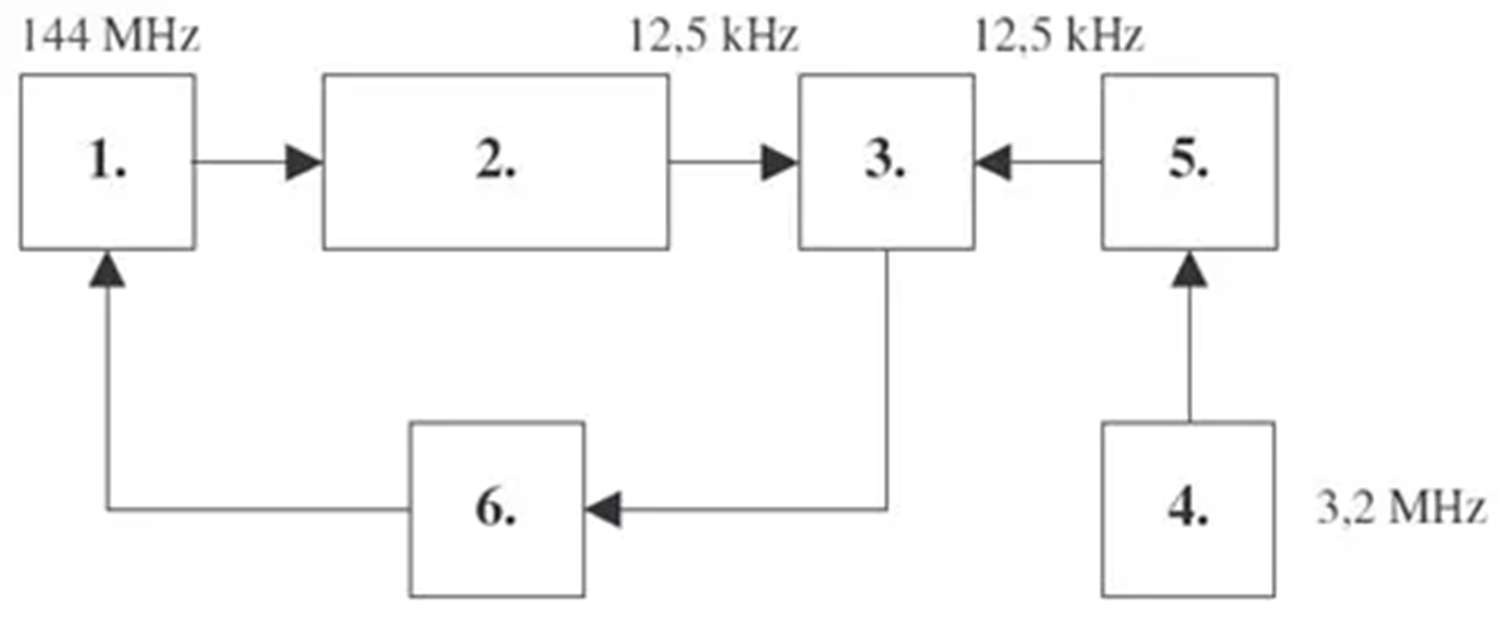

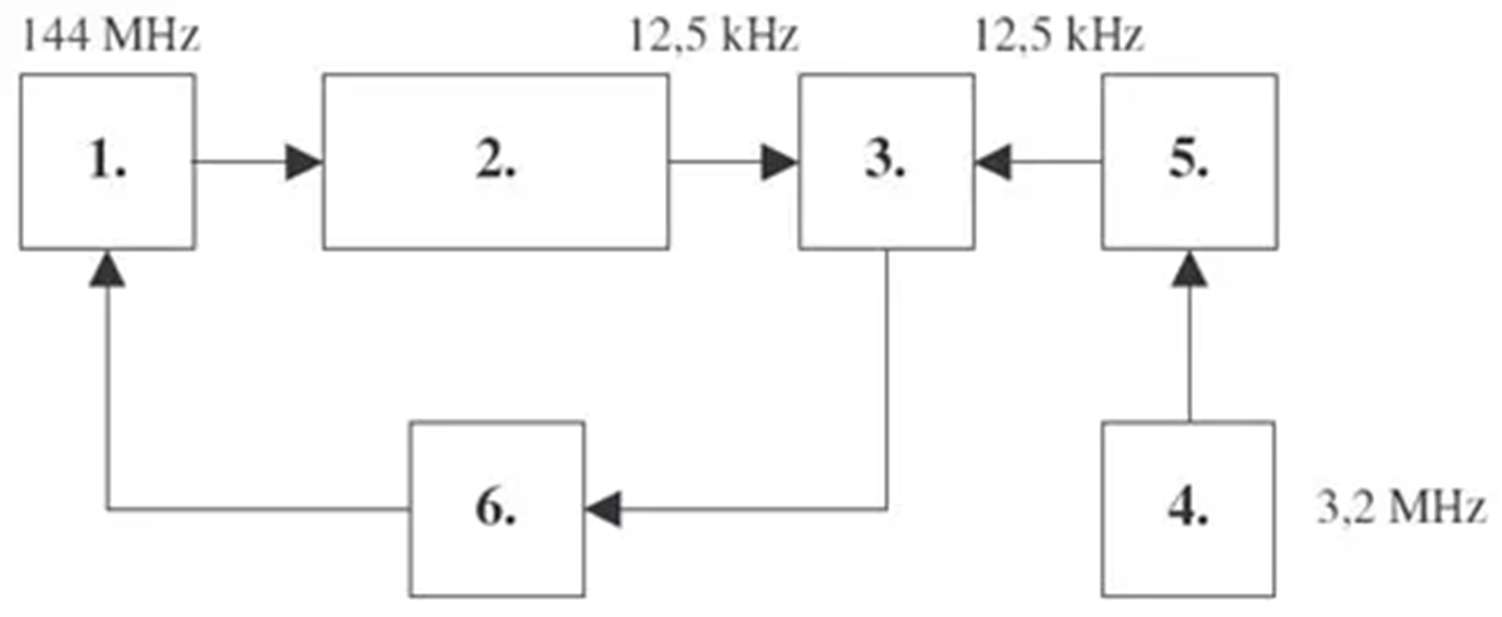

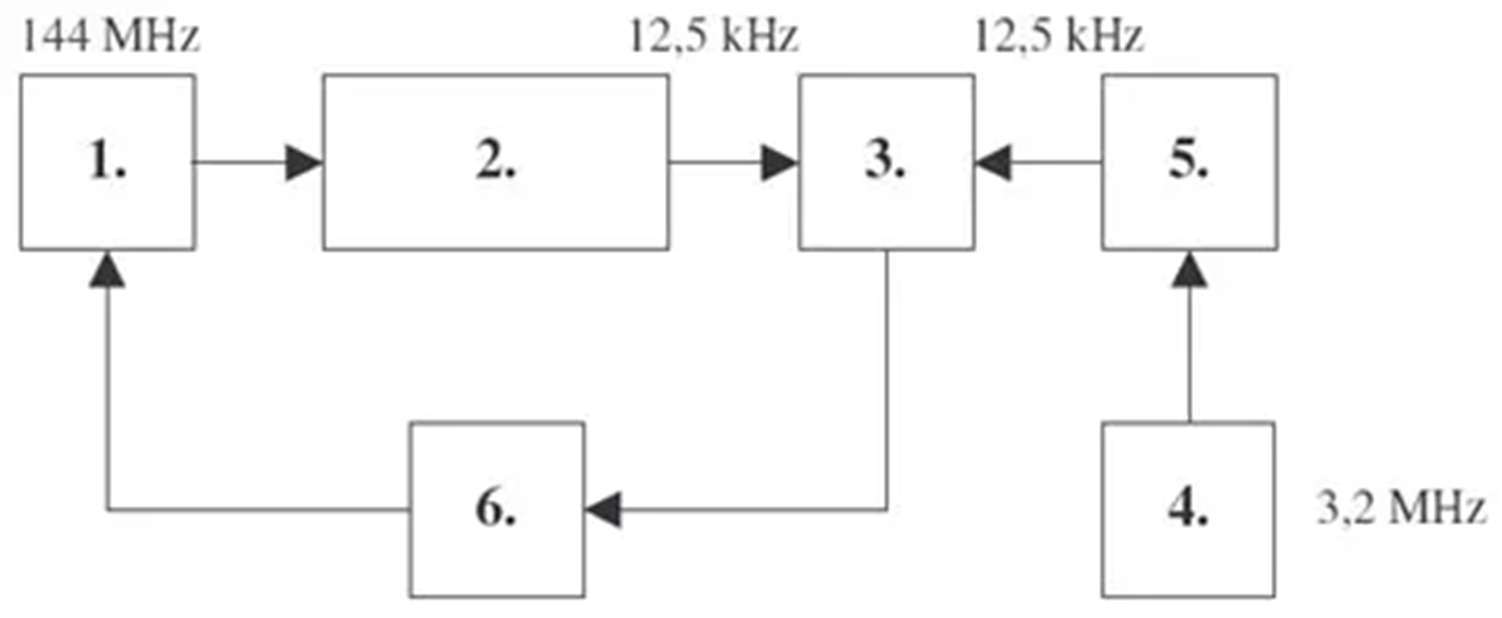

PLL to pętla sprzężenia zwrotnego: VCO (oscylator sterowany napięciem) generuje sygnał wyjściowy → dzielnik częstotliwości dzieli częstotliwość VCO przez N → komparator fazy porównuje z sygnałem wzorcowym (kwarc) → napięcie błędu koryguje VCO. Wynik: fVCO = N × fref. Zmieniając N (cyfrowo), zmieniasz częstotliwość wyjściową skokowo. Krok strojenia = fref (lub mniejszy z dzielnikiem ułamkowym).

Bloki PLL na egzaminie

Na schemacie blokowym musisz rozpoznać: generator stabilizowany (VCO) — produkuje sygnał wyjściowy, dzielnik częstotliwości — dzieli fVCO, komparator fazy — porównuje dwa sygnały, wzmacniacz błędu / filtr pętli — koryguje VCO, generator wzorca — stabilny kwarc (TCXO/OCXO), dzielnik wzorca — ustala krok strojenia.

Na egzaminie

VCO = generator sterowany napięciem (wyjście PLL). Komparator fazy = porównuje dwa sygnały. Dzielnik N = zmienia częstotliwość. Generator wzorca = kwarc (stabilność!). fwy = N × fref.

Gdzie szukać więcej

Chip: Si5351 — tani syntezator PLL, popularny w projektach amatorskich. YouTube: W2AEW — filmy o PLL. Projekt: VFO z Si5351 + Arduino — idealna nauka PLL w praktyce.